Dear Expert

In the process of debugging LMK04806, we met two problems, we would like to ask the original factory to help solve them.The detailed description is as follows:

1.PLL output cannot be locked, and LD_STATUS(PLL2_DLD) status indicator is flashing.The quality of power supply and input clock meet the requirements. We suspect that the configuration file is wrong, so we hope the original factory can help to provide a configuration file. The relevant conditions are as follows

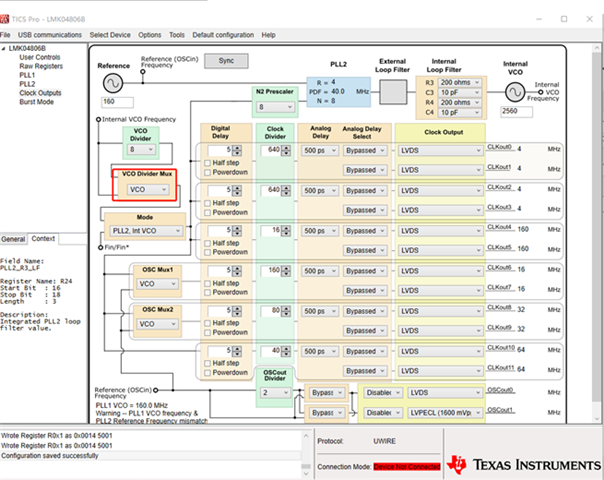

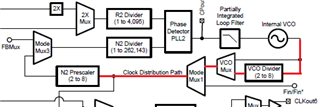

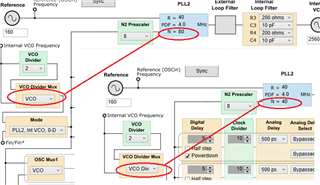

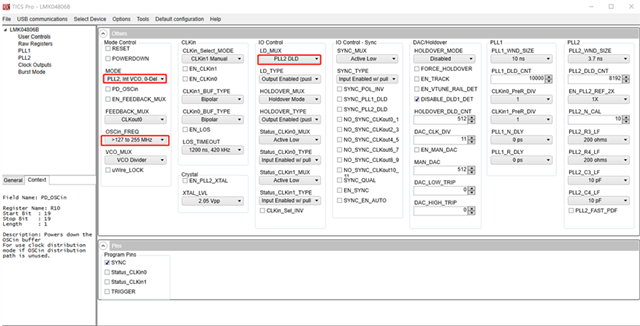

(1) Mode select PLL2, int VCO,0-delay;OSCin_freq is 160 m;No synchronization is required;The configuration interface is shown below. Please do not modify the ones circled in red. Anything else is OK.

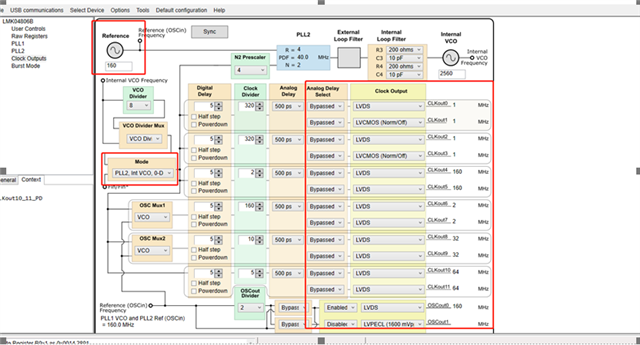

(2) The clock output interface is as follows. Please do not modify the part circled in red. The rest is OK

2. There is also a problem that the value of register R0 is not consistent with the value of register R0 written. The details are as follows:

(1) After power on, STATUS_Holdover is used as readback of uwire by default

Read R0:0x4000019

(3) R0:0x00142800

Read R0:0x50A00

Write R1:0x162801

(6) Read r1:0xb140

Hope you can reply as soon as possible. Thanks a lot!