Other Parts Discussed in Thread: LMK04832

Hi,

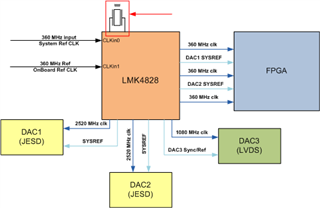

In our design, we are having clock requirements as per the below block diagram, currently planning to use the LMK04828 device for generating the clocks

We have the following queries on the same

- Is it possible to generate all the clock frequencies (as per the diagram) using the LMK device? What are your suggestions if any? Are there any conditions?

- In our design, we are providing 2 clock inputs, CLKin0 from a system clock source and CLKin1 from an onboard clock source, so these are the only clock sources available. In the LMK04828 datasheet, there is a "Simplified Schematic" diagram on page no 1, here what is the significance of "Crystal or VCXO" in the diagram? Do we need to provide a separate "Crystal or VCXO" clock source on the board?

Can you please provide your valuable inputs on our queries,

Thanks,

Kiran