Hi team,

What does the reserved bit in R31 mean?

The issue is PLL1 loses lock. We did 2 tests.

1. compare all the register readback, only R31 is different. please check the results below:

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi team,

What does the reserved bit in R31 mean?

The issue is PLL1 loses lock. We did 2 tests.

1. compare all the register readback, only R31 is different. please check the results below:

R0:0x140300

R1:0x140181

R2:0x140182

R3:0x140303

R4:0x140304

R5:0x140185

R6:0x11110006

R7:0x11110007

R8:0x11110008

R9:0x55555549

R10:0x1002410a

R11:0x40c300b

R12: 0xb0c01ac

R13: 0x1301866d

R14:0x100000e

R15:0x8010800f

R16:0x1550410

R24:0x883000d8

R25:0x1080019

R26:0x8fa0401a

R27:0x1c00201b

R28:0x10021c

R29:0x61d

R30:0x200061e

R31:0x9900103f //bad chip

R31:0xf900103f //good chip

2. ref clk is send to clockin0 in system, we connect a copy of ref clk to clockin1 and the chip is recover. All the regiter read back value is the same as good chip.

B&R

Lijia

Hi Noel,

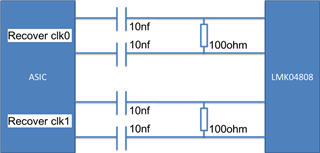

thanks for reply my question. I can't share the whole schematic to you. following are the clk in part:

this issue is happen only once, so I think clk in is not the trigger of it. Can you tell me what does R31 mean?(you can send me by email)

B&R

Lijia