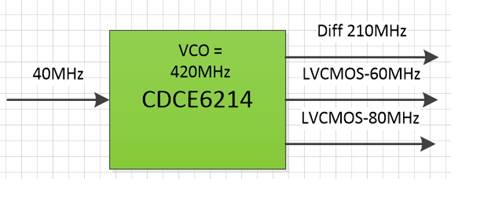

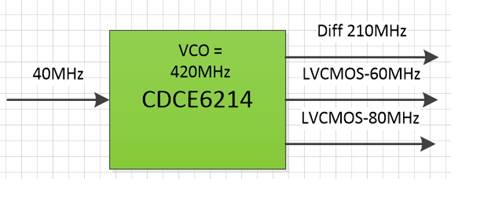

Here is the design block with CDCE6214 for FPGA usage in HMI application.

Could you check if this topology is ok or other suggestions? Very thanks.

Regards

Brian W

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Here is the design block with CDCE6214 for FPGA usage in HMI application.

Could you check if this topology is ok or other suggestions? Very thanks.

Regards

Brian W

Hi Brian,

Please use the Clock Tree Architect for part selection. https://www.ti.com/tool/CLOCK-TREE-ARCHITECT#:~:text=Clock%20tree%20architect%20is%20a,level%20multi%2Dchip%20clocking%20solution.

Regards,

Hao

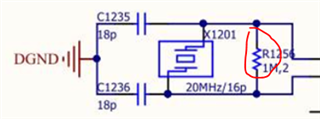

Thanks for help. Is there anything missing in the schematic below? Your suggestion is appreciate. thanks.

Hi Brian,

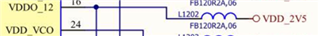

A few things:

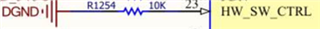

1. This resistor can be uninstalled (OK to keep the placeholder).

2. Is this VDDO set to 2.5V on purpose? This will lead to 2.5V CMOS on OUT2.

3. You'd want to pull this pin high to select EEPROM page 1, because EEPROM page 0 by default don't allow I2C access.

4. Add a placeholder for 0.1uF to ground (no need to install it) in case any delay is needed.

Regards,

Hao