Hi Team.

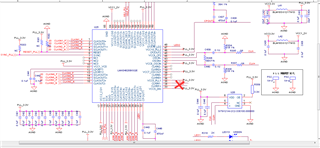

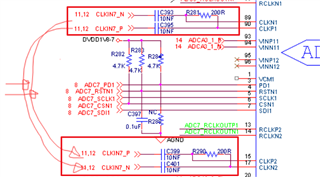

My customer now use 04828 in their project.

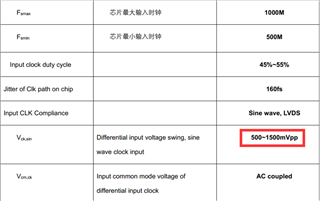

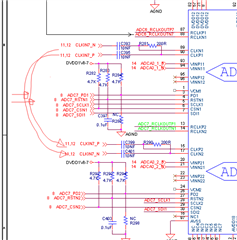

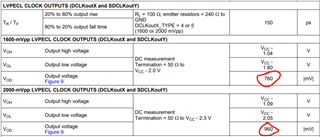

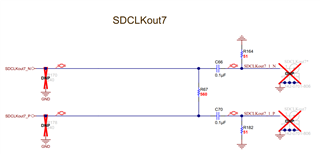

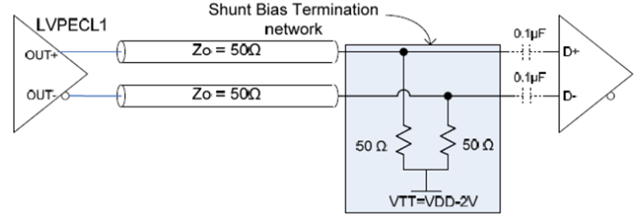

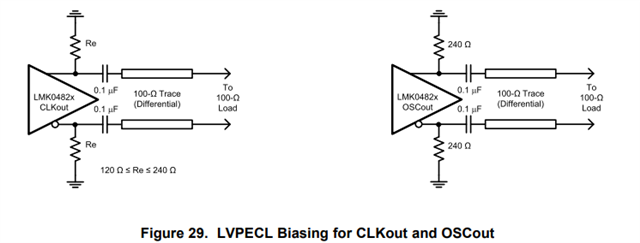

After setting the output in LVPECL mode, connect it to the ADC differential input (1 to 2) of two channels in parallel, and the clock amplitude is only 200mV. It is very low. And it is only about 400mV when it is 1to1. The single-channel clock of our downstream ADC channel needs at least 500mV or more.

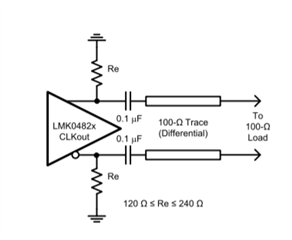

The hardware has been debugged a variety of peripheral impedance matching parameters, but they have not been improved.