Other Parts Discussed in Thread: ADS4222

Hello,

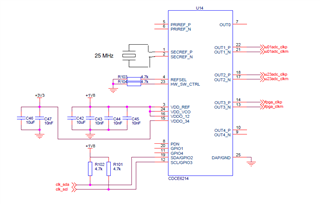

Below circuit was used to provide clock to FPGA and ADS4222.

And FPGA will use I2C to config this clock setting.

What's the initial clock output of below 5 channels before FPGA start any I2C?

Will it lead to a dead lock loop since it's a closed loop of FPGA clock input and FPGA I2C config?

Can FPGA start to work based on below initial hardware config when power on?