I am using the CDCLVP1102 (same family as the CDCLVP1204) to drive PCIexpress 100MHz reference to the input clock pins of Xilinx Virtex6 device. I have two questions:

- Where should I locate the AC coupling caps; near the source or near the target?

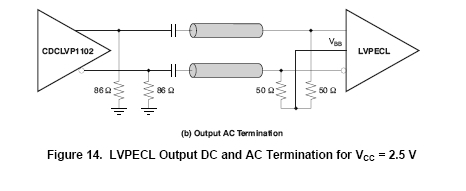

- Are the 50ohm Terminations after the AC caps shown in the Figure 14 of the data sheet needed for the CDCLVP part to be correctly terminated or only show there with the assumption that the next input device needs them to center the Common mode voltage to Vref?

Here are a few images from the respective data sheets.

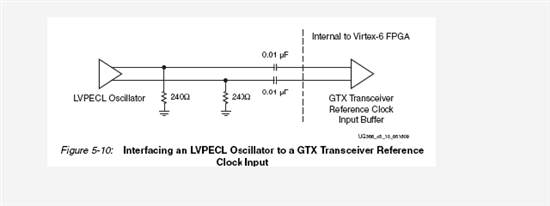

Xilinx requires AC coupled inputs as shown here.

The CDCLVP1102 data sheet shows:

Thanks, Al...