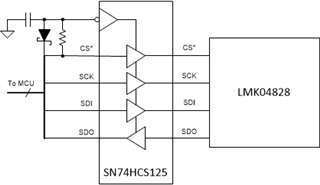

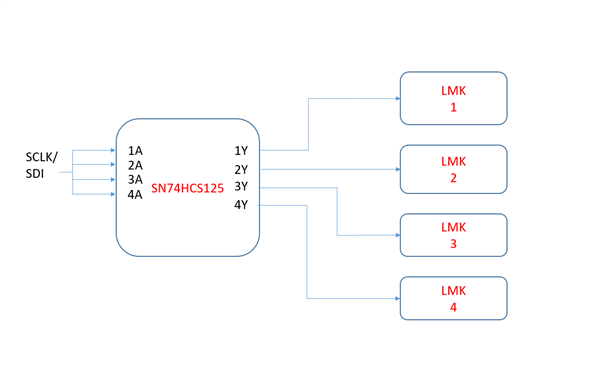

Part Number: LMK04828

Other Parts Discussed in Thread: SN74HCS125

Hello,

Could you please suggest techniques to mitigate high frequency noise on SPI lines. The details are below -

SPI frequency - 20MHz

Noise frequency ~1GHz @ -30dBc

Can we add RC filter for each SPI pin and place it close to the IC ? If yes, are there any drawbacks to this ?