Hi All,

I have a question regarding CLKin0/0* input in the LMK04828:

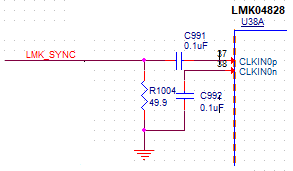

We drive it via AC coupling and in its MOS mode (CLKinX_TYPE=1).

CLKin0* is connected via a capacitor to GND.

We would like to bias it correctly, so when there is no activity on CLKin0/0* (AC coupling capacitors are in cut-off), there will be no false triggering (noise, etc.).

I don’t think I am allowed to connect a PU and PD on CLKin0 and CLKin0* respectively, since |VCLKinX-offset| states 55mV typical between these pins.

How should we handle this situation of biasing the inputs correctly for a no-activity situation?

Thank you!

Gil