Other Parts Discussed in Thread: LMX2594, LMK04208

Hi team,

I got a question from customer.

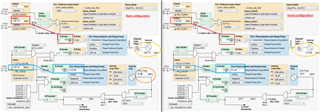

"I need to generate register set values for specifications i.e. reference clock=245.76 MHz and sampling rate=3.93216 Ghz .

With the reference of register values provided in the example code of SDK I am able to generate and match the register values for specification i.e. reference clock=122.88 Mhz and sampling rate =3.93216 GHz.

With the register values generated for 245.76 Mhz and sampling rate 3.93216 Ghz I am not getting any of the DAC's output on the spectrum analyser.

I am sharing the screenshots of LMK04208 and LMX2594 configurations and register set values generated along with this post.

Kindly see to it and correct me wherever I am going wrong."

Thank you very much for your help.

Best regards,