Part Number: LMK04828

Overview

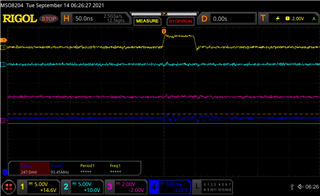

Our LMK04828 design intermittently fails PLL1 initial lock at startup. We are able to reproduce this failure if the LMK is “pre-warmed” up to a package temp of about 36°C from the last power cycle. If we power it up and the LMK’s package temp is ambient 25°C, the LMK achieves PLL1 lock and never loses lock, even if the package heats beyond 36°C. In the failed lock condition, PLL1_DLD, CP1Out, and the digital IO oscillate at some multiple of MHz frequency. We are seeking support from a TI engineer as the behavior seems to be not defined in the datasheet, and have provided the circuit schematic, LMK register settings, and scope shots.

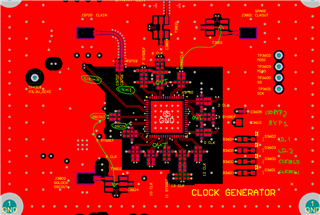

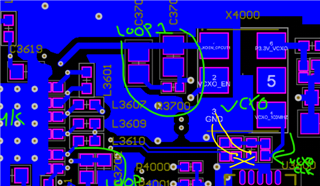

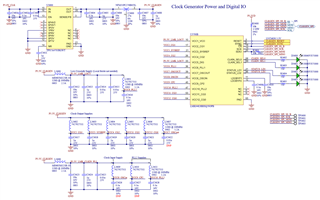

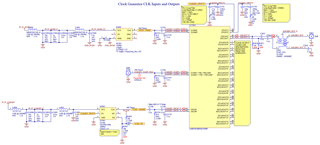

Schematic Design

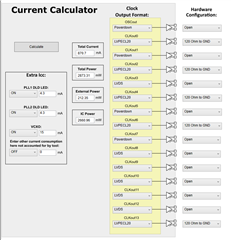

LMK Register Settings

R0 (INIT) 0x000090

R0 0x000010

R2 0x000200

R3 0x000306

R4 0x0004D0

R5 0x00055B

R6 0x000600

R12 0x000C51

R13 0x000D04

R256 0x01007E

R257 0x010122

R258 0x010255

R259 0x010305

R260 0x010462

R261 0x010500

R262 0x0106B0

R263 0x010706

R264 0x010868

R265 0x010922

R266 0x010A55

R267 0x010B05

R268 0x010C62

R269 0x010D00

R270 0x010EB0

R271 0x010F16

R272 0x01107E

R273 0x011122

R274 0x011255

R275 0x011305

R276 0x011462

R277 0x011500

R278 0x0116B0

R279 0x011706

R280 0x011861

R281 0x011955

R282 0x011A55

R283 0x011B01

R284 0x011C22

R285 0x011D00

R286 0x011E70

R287 0x011F06

R288 0x01200A

R289 0x012155

R290 0x012255

R291 0x012300

R292 0x012422

R293 0x012500

R294 0x012670

R295 0x012711

R296 0x012868

R297 0x012922

R298 0x012A55

R299 0x012B05

R300 0x012C62

R301 0x012D00

R302 0x012EB0

R303 0x012F11

R304 0x01301E

R305 0x013122

R306 0x013255

R307 0x013305

R308 0x013442

R309 0x013500

R310 0x0136B0

R311 0x013761

R312 0x013830

R313 0x013903

R314 0x013A02

R315 0x013B80

R316 0x013C00

R317 0x013D08

R318 0x013E03

R319 0x013F00

R320 0x014000

R321 0x014100

R322 0x014200

R323 0x014311

R324 0x0144FF

R325 0x01457F

R326 0x014608

R327 0x01470E

R328 0x014813

R329 0x014913

R330 0x014A00

R331 0x014B05

R332 0x014CFF

R333 0x014D00

R334 0x014E00

R335 0x014F7F

R336 0x015000

R337 0x015102

R338 0x015200

R339 0x015300

R340 0x015401

R341 0x015500

R342 0x015601

R343 0x015700

R344 0x01580A

R345 0x015900

R346 0x015A0A

R347 0x015BDF

R348 0x015C20

R349 0x015D00

R350 0x015E00

R351 0x015F0B

R352 0x016000

R353 0x01610A

R354 0x016290

R355 0x016300

R356 0x016400

R357 0x016504

R369 0x0171AA

R370 0x017202

R380 0x017C15

R381 0x017D33

R358 0x016600

R359 0x016700

R360 0x01684B

R361 0x016949

R362 0x016A00

R363 0x016B20

R364 0x016C00

R365 0x016D00

R366 0x016E13

R371 0x017300

R386 0x018200

R387 0x018300

R388 0x018400

R389 0x018500

R392 0x018800

R393 0x018900

R394 0x018A00

R395 0x018B00

R8189 0x1FFD00

R8190 0x1FFE00

R8191 0x1FFF53

R0 (INIT) 0x000090 R0 0x000010 R2 0x000200 R3 0x000306 R4 0x0004D0 R5 0x00055B R6 0x000600 R12 0x000C51 R13 0x000D04 R256 0x01007E R257 0x010122 R258 0x010255 R259 0x010305 R260 0x010462 R261 0x010500 R262 0x0106B0 R263 0x010706 R264 0x010868 R265 0x010922 R266 0x010A55 R267 0x010B05 R268 0x010C62 R269 0x010D00 R270 0x010EB0 R271 0x010F16 R272 0x01107E R273 0x011122 R274 0x011255 R275 0x011305 R276 0x011462 R277 0x011500 R278 0x0116B0 R279 0x011706 R280 0x011861 R281 0x011955 R282 0x011A55 R283 0x011B01 R284 0x011C22 R285 0x011D00 R286 0x011E70 R287 0x011F06 R288 0x01200A R289 0x012155 R290 0x012255 R291 0x012300 R292 0x012422 R293 0x012500 R294 0x012670 R295 0x012711 R296 0x012868 R297 0x012922 R298 0x012A55 R299 0x012B05 R300 0x012C62 R301 0x012D00 R302 0x012EB0 R303 0x012F11 R304 0x01301E R305 0x013122 R306 0x013255 R307 0x013305 R308 0x013442 R309 0x013500 R310 0x0136B0 R311 0x013761 R312 0x013830 R313 0x013903 R314 0x013A02 R315 0x013B80 R316 0x013C00 R317 0x013D08 R318 0x013E03 R319 0x013F00 R320 0x014000 R321 0x014100 R322 0x014200 R323 0x014311 R324 0x0144FF R325 0x01457F R326 0x014608 R327 0x01470E R328 0x014813 R329 0x014913 R330 0x014A00 R331 0x014B05 R332 0x014CFF R333 0x014D00 R334 0x014E00 R335 0x014F7F R336 0x015000 R337 0x015102 R338 0x015200 R339 0x015300 R340 0x015401 R341 0x015500 R342 0x015601 R343 0x015700 R344 0x01580A R345 0x015900 R346 0x015A0A R347 0x015BDF R348 0x015C20 R349 0x015D00 R350 0x015E00 R351 0x015F0B R352 0x016000 R353 0x01610A R354 0x016290 R355 0x016300 R356 0x016400 R357 0x016504 R369 0x0171AA R370 0x017202 R380 0x017C15 R381 0x017D33 R358 0x016600 R359 0x016700 R360 0x01684B R361 0x016949 R362 0x016A00 R363 0x016B20 R364 0x016C00 R365 0x016D00 R366 0x016E13 R371 0x017300 R386 0x018200 R387 0x018300 R388 0x018400 R389 0x018500 R392 0x018800 R393 0x018900 R394 0x018A00 R395 0x018B00 R8189 0x1FFD00 R8190 0x1FFE00 R8191 0x1FFF53

Experiments

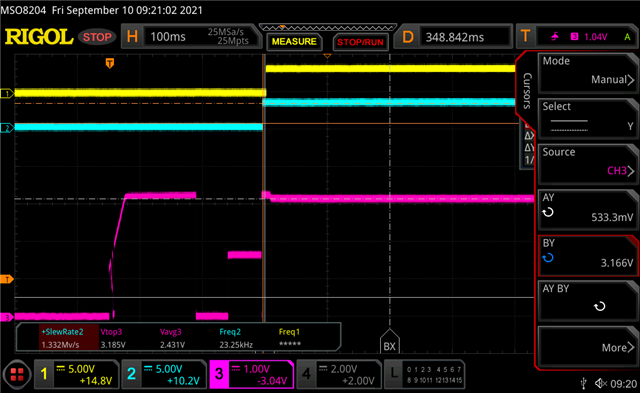

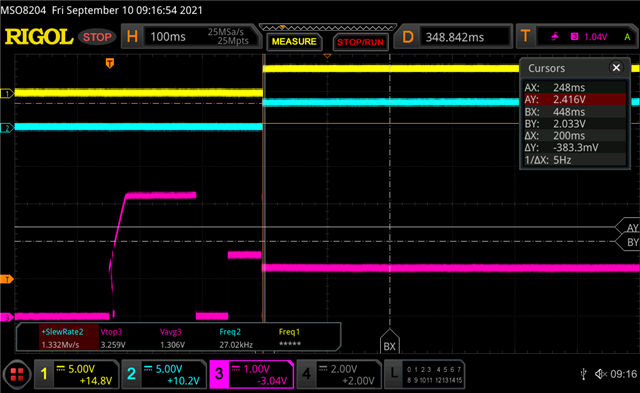

We started by determining the condition in which PLL1 goes unstable and does not lock. The failure seemed temperature dependent so we began by cooling IC’s with canned air in an attempt to find which IC is sensitive and where the threshold is. We found that when the LMK04828’s package starts above 36°C and the LMK is powered on, PLL1 will not lock. This test was repeated with a hot board and a small heat gun, warming the IC. Interestingly, if the LMK is powered on while it is cold it locks instantly and maintains lock well above 36°C.

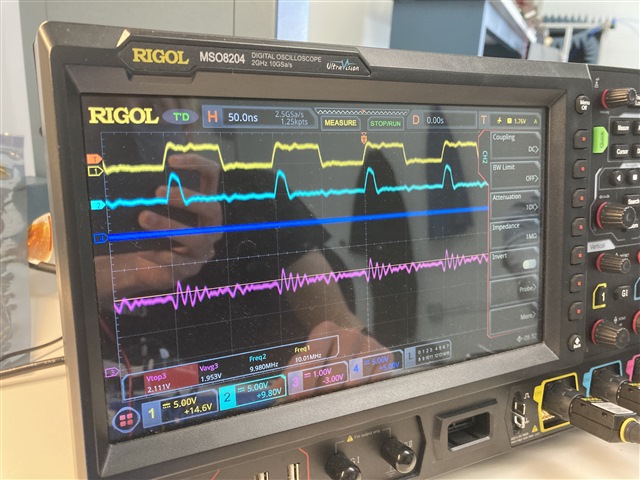

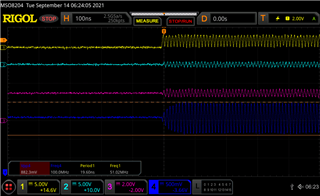

When the LMK fails to lock, the Status_LD1 I/O assigned to the PLL1_DLD lock state oscillates at either 100MHz, 10MHz, 5MHz or other whole number divisions of 100MHz. With our PLL1_WND_SIZE set to 43ns and PLL1_DLD_CNT set to 8192 we don't believe the LD1 PLL1 lock output should be able to switch states at anywhere near these frequencies if the datasheet is correct. We worry that the LMK is entering an undefined state or a feedback loop, of which we have no clear solution. It feels pertinent to note that in this state the LMK’s digital outputs and inputs (SPI and LD1/LD2) have significant noise present at the same frequency when in the fault condition.

We have checked the LMK’s 3V3 supply, it is clean and provided by a local low noise LDO (TPS7A4701). The filtering into the VCC pins for the various supplies on the LMK are decoupled with appropriate capacitors and filtered with appropriate low series resistance ferrites. The decoupling scheme to our knowledge aligns with the recommendations in the datasheet. We additionally tried powering the VCXO from a different supply than the LMK’s supply and found the same behavior was present.

Our reference OCXO (±50ppb) is powered from another separate LDO supply and conforms to slew rate and voltage requirements. Our VCXO (±50ppm absolute pulling range) also conforms to slew and output voltage requirements. It has a max pulling range of 50ppm and in normal operation does not thermally drift more than 18ppm (calculated by differencing the hot and cold PLL1 control voltage as well as the ppm/V values).

We have attempted multiple loop filter R C configurations for bandwidths, 100hz, 1000hz, and 20khz (the schematic shows Loop Filter PLL1 for 100hz). All calculated with the PLLatinum Sim. The response of the PLL seems appropriately damped when it manages to lock, leading us to believe our loop filter is appropriately tuned.

We have disabled the reset input in an attempt to remove the possibility of it responding to noise and resetting the LMK. We have holdover disabled, PLL delays disabled, and no sync or clock source switching enabled. We tried lowering PLL1’s detect frequency from 10Mhz to 1Mhz with a divider change and found the same fault. We also tried powering down the entire DCLK/SDCLK output stage and found the same fault.

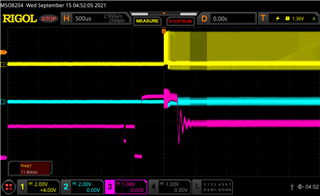

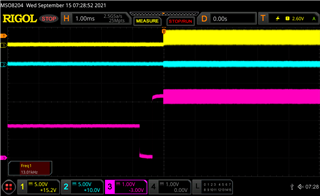

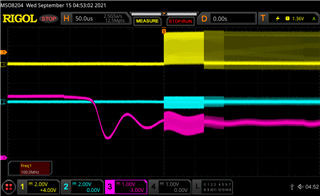

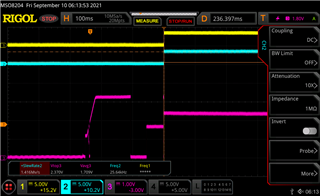

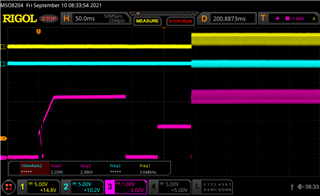

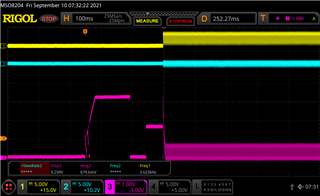

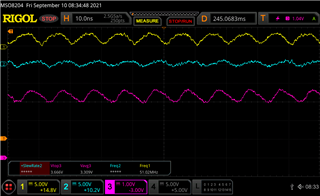

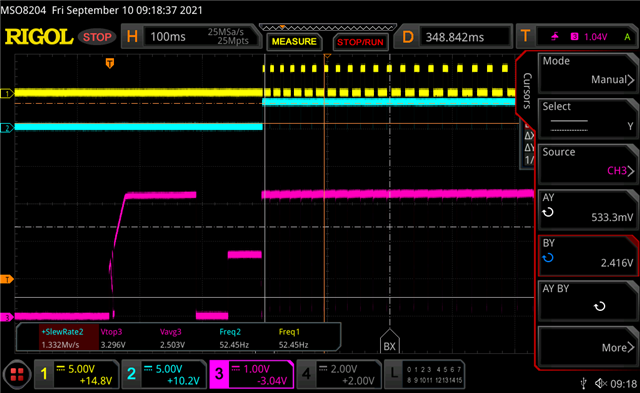

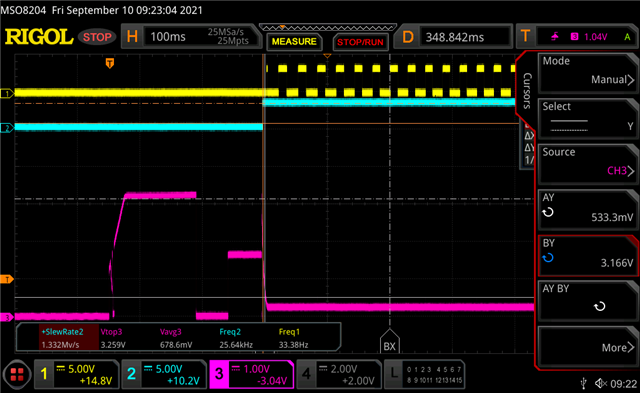

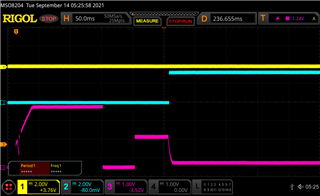

For all Scope Captures:

Trace 1 - LD1(PLL1 lock)

Trace 2 - LD2(PLL2 lock)

Trace 3 - PLL1 control voltage output

Capture of a successful lock with a room temperature board (RigolDS0.png)

Failure to Lock (Control voltage drifts up to 3V3) (RigolDS18.png)

Failure to Lock (Control voltage drops to close to 0V) (RigolDS7.png)

Failure to lock (finer timescale) (RigolDS20.png)

.

.