Hi teams,

We use NXP Processor to control LMK 04832, its SPI is 4-wired SPI, especially DMA control, the minimum transmission SPI data is 4 bytes (32bits), but LMK04832 programming is 24-bit register, so we fix the programming register at the end One byte is filled with 0.

Will this cause the LMK04832 register to be written abnormally? Please suggest how to handle the communication between different devices of SPI configuration?

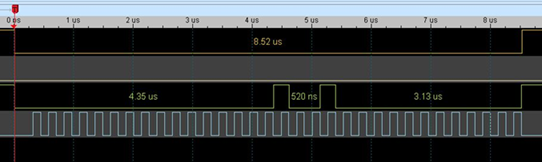

The following picture shows writing value 0x90 to register addr 0x00, the bottom is SCK, the top is SDIO, the top is CS, and you can see that should be sent 24-bit (2bytes addr, 1byte data) to SDIO, but NXP Processor's SPI sent a total of 32-bit data to SDIO.

Thanks.