Hi Ti-Support,

I have just a vewry simple question (I think)

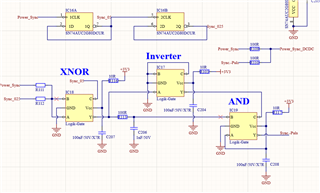

I want to make a very simple clock divider for an application with an D-Fli-Flop. SN74AUC2G80DCUR

The circuit is very simple and work theoretical, but not practical ;-)

The output from the D-FF will be connect to the D-Input and so on.

For short it do not work, I guess I need some delay for the feedback (RC combination).

Or is this not possible with this device.

Regards

sascha