Other Parts Discussed in Thread: LMK04610

Hello,

We are evaluating the LMK04610 but I am having issues with the evaluation module. I’m using a 100 MHz source, and trying to get a 100 MHz output bypassing the VCXO.

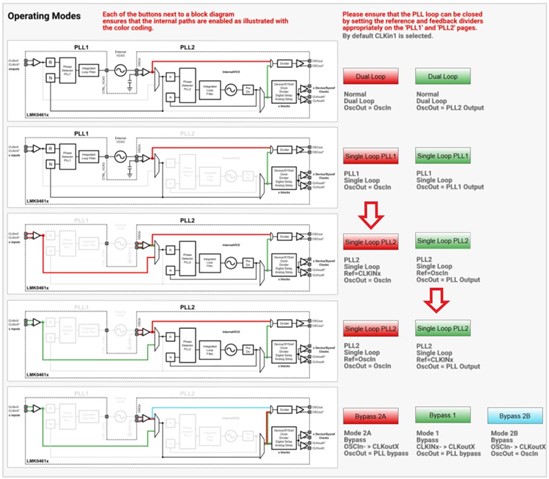

I’m selecting either of these 2 modes:

When I look at the PLL2 Reference clock using the mux on the status pin, I see it. But, I am not getting a clock out.

There is a bug when using the Frequency Planer where is doesn’t write the dividers to PLL1. I got it to work by changing them using the PLL1 control screen.

What can I provide to help you help me?

Thanks,

Adam