Hi team,

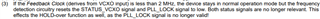

VCO indicators:

Output frequency: 384MHZ

Output power: 1.5 ~ 4.5dBm

Tuning voltage 0.5 ~ 2.5V

Voltage control sensitivity: 3-6MHZ / V

PLL settings:

Output clock: 384MHZ, 96MHZ, 24MHZ

Reference clock: 100MHz

Problem: the STATUS_VCXO pin of CDCM7005-SP of two of the six boards indicates abnormity at low temperature of - 10 ℃, and the locking indication is also abnormal. However, there is no problem with the output clocks of 384MHZ, 96MHZ and 24MHz of the test chip, which proves that the PLL locking is normal, and only the status indication is abnormal. No problem at room temperature.

The loop bandwidth is changed to 100k, and the problem still exists.

What could be the problem?

Best Regards,

Amy Luo