Hi:

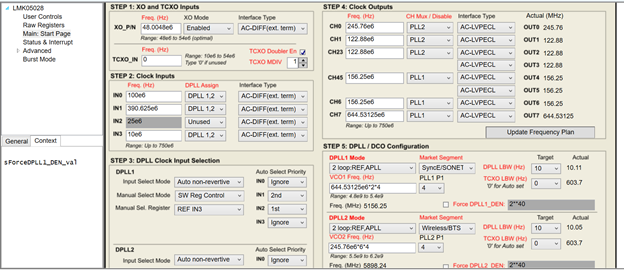

I am working on the Intel S10 SX SoC Dev Kit . LMK05028 chip is mounted on the board. The TCX0_IN is not driven by any clock. The IN3 is driven by 10Mhz from GPS. My requirement is that OUT7[644.53125Mhz], OUT5[390.625Mhz] should be generated from GPS 10Mhz as reference .The OUT5 and OUT7 are connected to FPGA. The OUT7 clock is the reference clock for the MAC inside FPGA.

DPLL1 and DPLL2 priority of clock is same. 10Mhz[IN3] has highest priority.

I have configured TISC Pro with below configuration. We are not getting required output that is 644.53125Mhz instead we are getting 644.46Mhz. And OUT5 if I configure 390.625Mhz actual frequency column in GUI become zero. Could you please guide me to get the OUT7 and OUT5 with proper output and frequency in sync with GPS 10Mhz.