Part Number: LMK05028

Hello,

We are currently using LMK05028 to generate 122.88MHz in 3 loop mode with 20MHz TCXO and 48MHz XO from an 1Hz (GPS PPS).

We are facing issue to get the ref0 to validate.

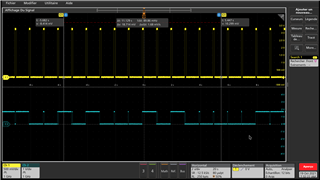

I measured the PPS and the STAT0 output (with REF0 monitor div out div by 2). It's never stable, ref0 validation is unstable.

(PS: If i enable the 1-PPS Jitter threshold, ref0 never validate at all).

Could you help me out?

THanks you very much.

Cyril.

Please find attached the configuration file.6330.config.tcs