HI team,

In our Design we are using 5 LMK'S .One LMK acts as master and remaining 4 LMK'S acts as Slaves.

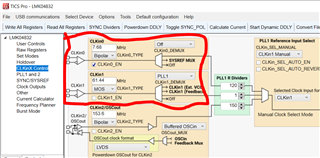

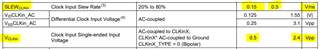

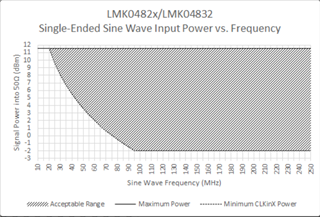

Master LMK input Frequency : 49.152 MHz

Master LMK output Frequency : 7.68 MHz

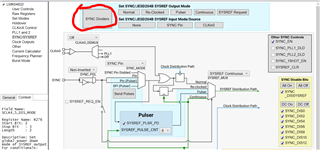

Which mode i need to prefer ? AS of now i am using Dual loop mode .so Please go through the tcs file and schematic and suggest me regarding the mode.

And in master we are getting CPout as 3.2V but as per data sheet (VCC/2).

Note : Loop filter same as evm

But still we are having issue with PLL1 lock issue .

Slave is in Dual loop Nested mode .