Hi everyone,

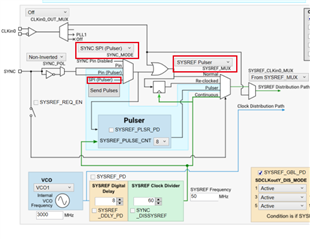

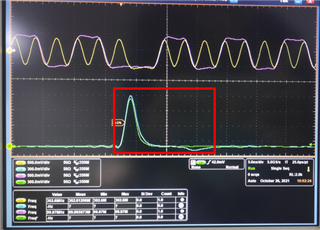

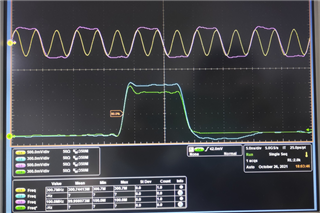

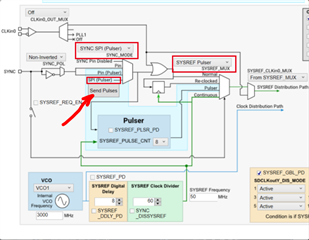

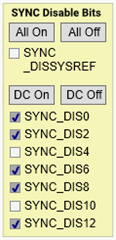

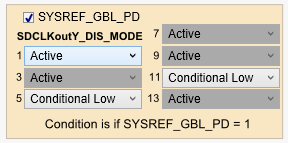

I met a new problem when I config SYSREF signal with 'SYNC SPI (Pulser)' mode(Figure 1), but when I catch the signal the SYSREF changed like a spur with overshoot at the falling edge(Figure 2) although the device clocks are sync. When I disable the SYSREF, the siganl is normal(Figure 3). I don't understand why?

PS: I use 10MHz oscillator as PLL1 input.