Hello TI forum,

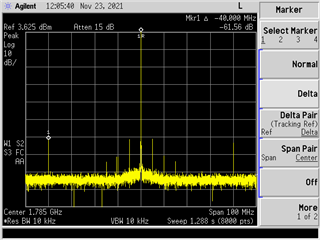

Should the VCO Phase Sync feature increase phase detector spurs? I am generating a carrier at 1785 MHz with Channel Divider = 6 and IncludedDivide = 1 and getting great noise and spur performance. Fpd spurs at +/- 40 MHz are around -90 dBc. When I check the VCO_PHASE_SYNC box the IncludedDevide changes to 6 as expected and the fpd spurs increase about 20 dB. Can this be avoided? Help!

Best regards,

Mike Biggs