Hello.

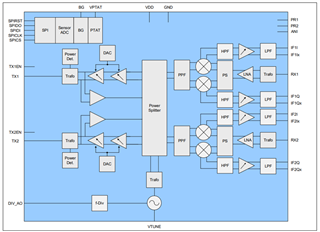

LMX2491 CHIP related question.

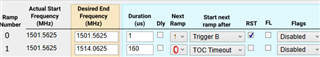

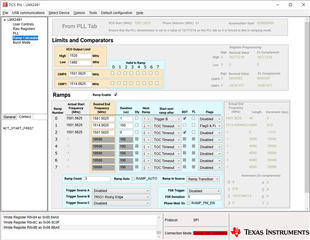

Ramp length is set by register settings.

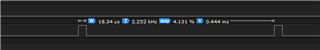

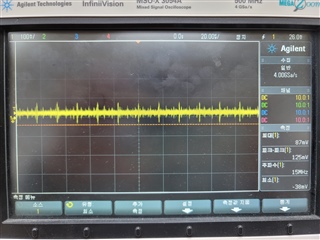

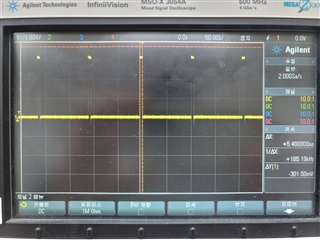

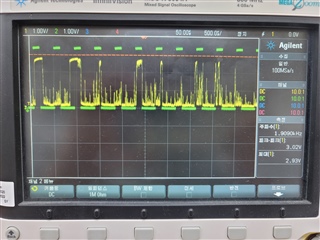

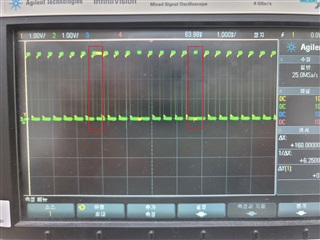

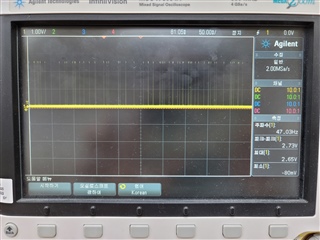

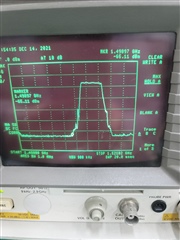

I set a value of 160us, but when I look at the TRIG value, I get 16us.

I don't know why.

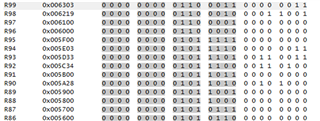

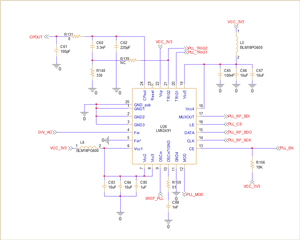

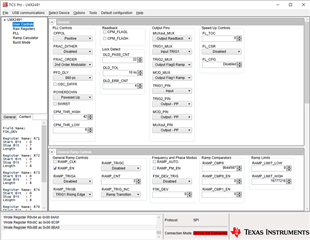

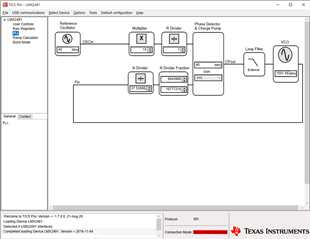

Below is the register setting value.

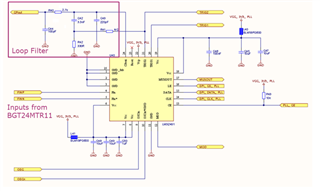

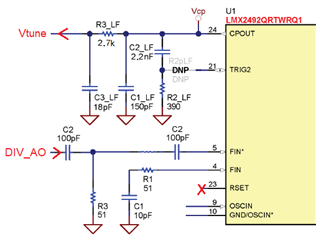

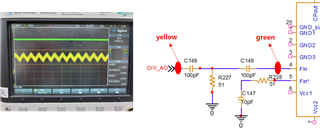

And there is no output to CPOUT either.

So I was wondering if there is something wrong with the register settings.

R106 0x006A04

R105 0x006900

R104 0x006800

R103 0x00673F

R102 0x0066FF

R101 0x0065FA

R100 0x0064E2

R99 0x006343

R98 0x006219

R97 0x006100

R96 0x006000

R95 0x005F00

R94 0x005E03

R93 0x005D33

R92 0x005C34

R91 0x005B00

R90 0x005A28

R89 0x005900

R88 0x005800

R87 0x005700

R86 0x005600

R85 0x005500

R84 0x005400

R83 0x005303

R82 0x005201

R81 0x005100

R80 0x005000

R79 0x004F00

R78 0x004E00

R77 0x004D00

R76 0x004C00

R75 0x004B00

R74 0x004A00

R73 0x004900

R72 0x004800

R71 0x004700

R70 0x004600

R69 0x004500

R68 0x004400

R67 0x0043DA

R66 0x004202

R65 0x004175

R64 0x004000

R63 0x003F00

R62 0x003E8A

R61 0x003D02

R60 0x003C75

R59 0x003B01

R58 0x003A01

R57 0x003900

R45 0x002D00

R44 0x002C00

R43 0x002B00

R42 0x002A00

R41 0x002900

R40 0x002800

R39 0x00273A

R38 0x0026FA

R37 0x0025F2

R36 0x00240F

R35 0x002341

R34 0x002284

R33 0x002120

R32 0x002000

R31 0x001F2A

R30 0x001E06

R29 0x001D00

R28 0x001C1F

R27 0x001B08

R26 0x001A00

R25 0x001901

R24 0x001800

R23 0x001700

R22 0x001600

R21 0x00158A

R20 0x001400

R19 0x001300

R18 0x00122C

R17 0x001100

R16 0x001025

R15 0x000F00

R14 0x000E00

R13 0x000D00

R12 0x000C00

R11 0x000B00

R10 0x000A00

R9 0x000900

R8 0x000800

R7 0x000700

R6 0x000600

R5 0x000500

R4 0x000400

R3 0x000300

R2 0x000201

R1 0x000100

R0 0x000018