Other Parts Discussed in Thread: LMK00306

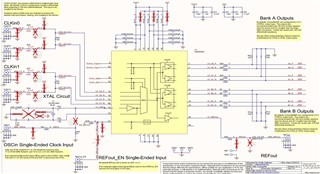

I want to use the LMK00304 & LMK00306 buffers, but the datasheet doesn’t specifically indicate if the part has internal DC biasing.

I am hoping you can provide clear guidance on connecting this part.

- Is this DC biased internally?

- If not, is there a recommended biasing?

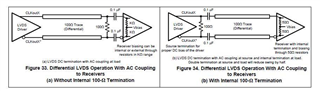

- If AC coupled, LVDS input:

- Is a 100ohm between the differential nets all that is needed?

- Should that 100ohms be on the IC input side of the AC coupling?

Also, the termination Figures 33 & 34 in the datasheet don’t match to what I would expect. I downloaded the eval board schematic for this part, but it looks like it was reworked and doesn’t match the datasheet… actually matches what I would expect.