Hi sir,

I wanna confirm how to use SYNC pin (action on Distribution Mode) for LMK04832NKDR.

please find the attachment.

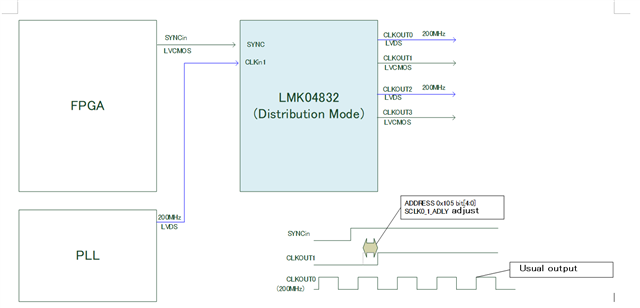

FPGA → connect to LMK04832 SYNC pin

PLL → input 200MHz LVDS to CLKin1

Can I adjust the output delay of the FPGA as above?

Thanks.

Regards,