Hi team,

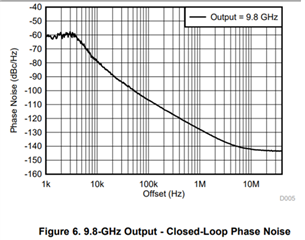

My customers are trying lower loop bandwidths with the LMX2592. The datasheet has the following plot showing a ~4kHz closed-loop bandwidth:

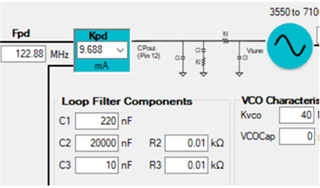

What loop filter component values were used for this test?

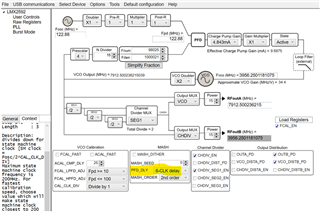

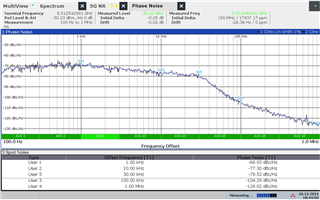

Customer is trying large capacitors in the loop filter and seeing large loop gain changes with small frequency adjustments. PLLatimumSim does not show the gain variations they’re measuring. Higher loop bandwidths (~ 100kHz) do not show this issue.

Thanks,

Connie