Helllo E2E,

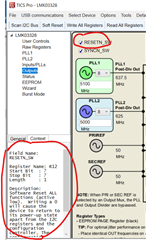

What are the terms need to be applied for the PLL to run automatic VCO calibration on power up?

The reason I’m asking it is because currently what we did is burning the PLL to its internal EEPROM, and the values for the PLL are constantly loaded from the EEPROM each power up.

The PLL provide ref clock for an FPGA.

When the PLL load parameters from EEPROM after power up everything work good.

When we tried to change the PLL output divider (and of course changing the parameters on the FPGA to fit to the new clock) it didn’t work.

We add VCO calibration after power up, before changing the output divider and then the system began to work.

Can you explain what else is been done while we preform VCO calibration?

Thank you!

Russell