Hi all

Would you mind if we ask LMK05318?

Could you refer to the .tcs file and scope figures?

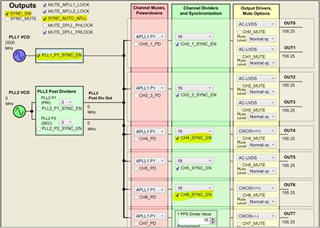

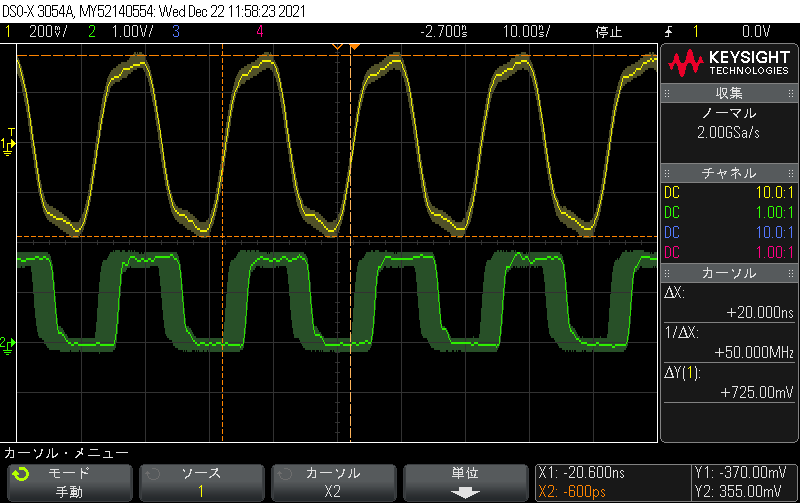

■1__EVM-default__Select-PLL2__211220.tcs■

OUTPUT0~7 156.25MHz with PLL2 VCO, LMK05318's EVM

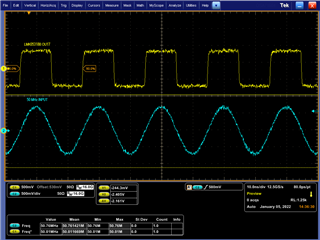

→ We got scope_9.bmp, it seems that input is synchronized with output.(OK)

(scope_9.bmp is overlapped display with several wave forms.)

■2__EVM-default__OUT-Freq25M__211220.tcs■

OUTPUT0~7 25MHz with PLL1 VCO, LMK05318's EVM

→ We got scope_13.bmp, it seems that input is synchronized with output.(OK)

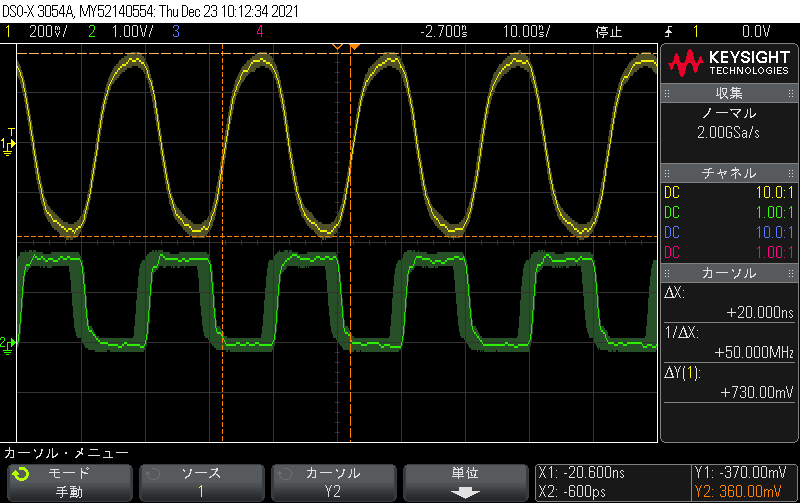

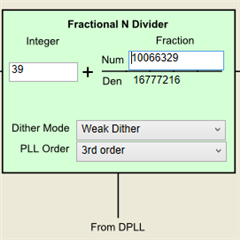

■3__EVM-default__OUT-Freq25M__Select-PLL2__211220.tcs■

OUTPUT0~7 25MHz with PLL2 VCO, LMK05318's EVM

→ We got scope_14.bmp, it seems that input is not synchronized with output.(NG)

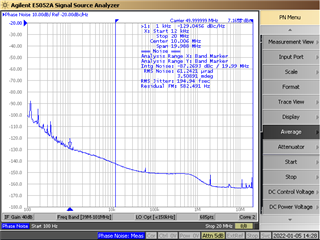

So, we don't understand why input is not synchronized with output and it seems that jitter increases.

If you have some advice, could you let us know?

We assume that it is possible to confirm these using EVM.

*On the TICSPRO operation, the customer executed Calculate frequency -> Run scriprt in any case.

20211221_Scope9, Scope13, Scope14.pdf

1__EVM-default__Select-PLL2__211220.tcs

2__EVM-default__OUT-Freq25M__211220.tcs

3__EVM-default__OUT-Freq25M__Select-PLL2__211220.tcs

Kind regards,

Hirotaka Matsumoto