Part Number: LMK05318B

Hi all

Would you mind if we ask LMK05318B?

We attach the .tcs file

20220113_REF-54M053998__OUT7-54M053998__220113.tcs

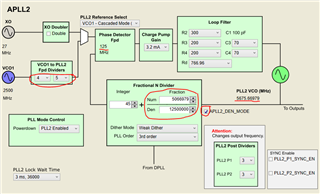

In case of operating Run Script on Set DPLL, it shows error message.

Warning: The input contains a value greater than the maximum contiguous flint.

(In our OS, it is showed by japanese, so the spells might be not correct.)

Could you let us know how to modify it?

Kind regards,

Hirotaka Matsumoto