Other Parts Discussed in Thread: CDCE62002, SRC4392, PCM1792A

Hi,

I have seen the recent update to the datasheet for the CDCE62002, and i have a few questions.

REF_IN- Connection

In error i connected the Oscillator to the negative pin of Ref - the REF_IN- which is pin 30, and tied low the Pin 29 - As i have selected CMOS.

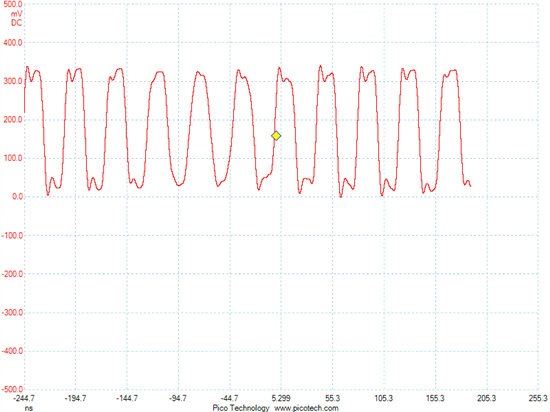

My USB Oscilloscope has a fault on it - so cannot guarantee the outputs - which are set to CMOS.

Is the connection of the REF_IN- pin to the oscillator an issue as the waveform output by the oscillator (24.576MHz) is not looking optimal - positive plateau seems to be ok, but negative is nearly a saw tooth. I have about 3mm of ground plane along one side of the track and obviously tracks either side after this as IC dimensions dictate this for 2mm to 3 mm.

AUX_IN Connection

I have connected a 28.224MHz crystal to the AUX_IN connection. There is a ground plane either side of this track for 7mm before the track is free besides other side tracks to the pin connection. Again, the USB Oscilloscope has a problem, but i do not see any signal on this pin at all - i would have expected there to be some voltage waveform. I believe i had programmed at the time of measurement that the CDCE62002 is to use the AUX_IN pin, so a waveform should be seen ?.

I am not seeing any output on the CDCE62002 and the PLL_LOCK pin seems to indicate a lock issue - hence is the Oscillator waveform too distorted for an adequate reference, and is the track layout for the crystal input outside tolerances for the use of the AUX_IN use - not asking for definitive yes or no, but guidance if this could most probably be the issue. Thanks.

Regards,

Richard