Hi all!

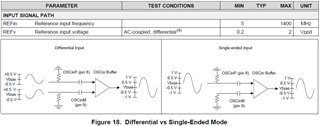

I see from the datasheet, As long as the Vppd falls between 0.1 to 1 for a differential signal, or 0.2 to 2 for a single-ended signal, the device will operate as defined on the datasheet.

From customer's experience with other PLL designs, there can be a sweet spot in the input power range that has a small effect on the performance of the device. Right now they use a 100MHz crystal but there is an opportunity to change it to a 150MHz version. In either case, there's option to adjust the reference power into the LMX2592 if it was determined that there was an optimal range of input powers.