Other Parts Discussed in Thread: LMK04906

Hi,

Can I use the digital delay on top of the 0-delay mode in the feedback clock to obtain phase advance of other outputs compared to input clock?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Joe,

When there is an delay in the feedback path using 0-delay mode, feedback path clock output in phase with CLKin and can have a phase difference between other clocks out based on delay in feedback path.

As mentioned in section 8.3.10 in datasheet, during the 0-delay mode, lowest frequency clock out should used for feedback to ensure fixed CLKin to CLKout phase relationship.

Thanks!

Regards,

Ajeet Pal

Hi Ajeet Pal,

If I off the osc doubler and move the N-divider value to output divider of feedback path, the feedback clock will always be the lowest frequency.

In this case, I can achieve the repeatable fixed CLKin to CLKout phase relationship between all clock outputs using internal 0-delay mode even though I use digital delay in the feedback path?

Hi Joe,

Would it be possible to share .tcs configuration file for your required frequencies to look on it in details?

Thanks!

Regards,

Ajeet Pal

Hi Ajeet Pal,

I don't have the actual hardware to test now but here I attached the .tcs configuration file.

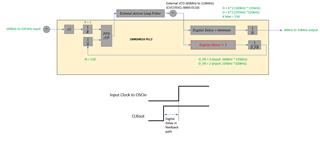

To simplify, is this what I can expected:

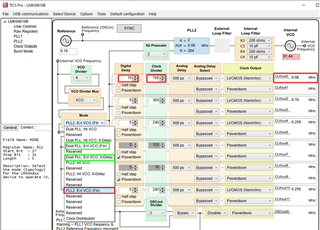

However, I have questions about how to properly configure the external VCO mode in TICS PRO.

I noticed that there are 2 modes to select for dual PLL with external VCO, which are non and zero-delay.

For single PLL2 with external VCO, there is only 1 option. Does it mean it must be the internal zero-delay mode?

The CLKOutx are always reflecting according to internal VCO in TICS PRO and I don't see a box to key in frequency for external VCO.

Is this because there won't be calibration for external VCO as with internal VCO?

Hi Joe,

Based on section 8.4.2.4 in datasheet, single PLL 0-delay mode with external VCO should also be possible, but somehow this option is not showing in TICS Pro.

That's correct, TICS Pro is reflecting only for internal VCO settings and to have external VCO need to be tweak on the other registers.

Like you did, it seems to be correct but you may need to manually write the PLL2_N (N - feedback divider) and PLL2_P (pre N-divider) based on your external VCO frequency in 0-delay mode.

Regarding your query to provide the feedback division for 0-delay using the channel divider and keep N --> 1, it is not be possible as PLL2_P divider has minimum divide value 2 and that would be present in feedback path.

Also the digital delay in feedback path would be consider after sync operation and NO_SYNC_CLKoutX_Y bit set to 0. Follow the section 8.6.3.4.3 in datasheet.

I would be suggesting to order an EVM and can try with your required frequencies.

Thanks!

Regards,

Ajeet Pal

Hi Ajeet Pal,

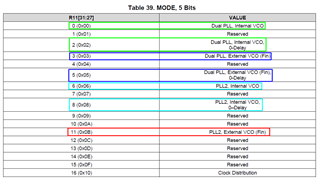

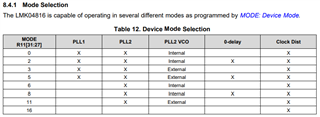

I wonder how should I set to "PLL2, External VCO (Fin), 0-delay" as it is not included in the available mode in R11[31:27].

Do you have any idea?

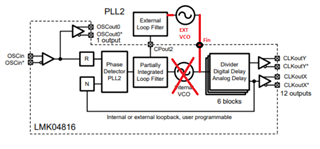

From block diagram, The PLL2 N Prescaler should not matter anymore if using External VCO with 0-delay as it is not in the feedback path for 0-delay and calibration routine is bypassed for external VCO.

Hi Joe,

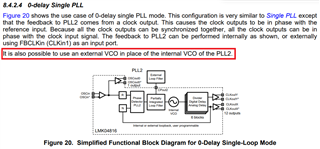

It should be same as figure 20 in datasheet except external VCO and feedback would be through N-divider for 0-delay also.

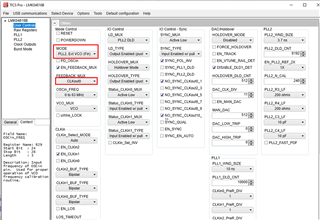

As you mentioned above correctly, set the mode (0x0B) for "PLL2, External VCO" and enable the feedback mux with CLKout0. Later set the N-divider manually based on channel divider value. Yes, PLL2_N prescaler will be away from 0-delay feedback path.

Thanks!

Regards,

Ajeet Pal

Hi Ajeet Pal,

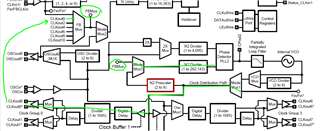

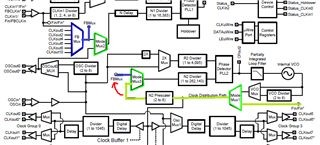

I think by setting the mode to "PLL2, External VCO" will only turn on the green path.

And by enable the feedback mux will only turn on the FB Mux (Blue color).

Probably still need some kind of "MODE" setting to switch the Mode Mux3 from internal path to feedback mux path (red arrow)?

Unfortunately I am still waiting for complete hardware to verify this.

Can you confirm LMK04816 is able to implement "PLL2, External VCO with 0-delay' or the software is not supported for this mode yet as it is not listed in MODE Table 39?

Hi Joe,

TI has not tested with external VCO in 0-delay single PLL mode and I also don't have the HW with external VCO on board to verify.

Even the datasheet doesn't show any mode with same configuration.

While changing the mode from "PLL2, Int VCO, 0-delay" to "PLL2, Ext VCO" and 0-delay; Mode Mux 3 is not clear and that could be the reason Ext VCO 0-delay mode is not defined.

As it is not defined, TI would not recommend in this configuration.

I am checking from the design side the possibility of this mode and will update you soon.

Thanks!

Regards,

Ajeet Pal

Hi Joe,

Sorry for delay in response.

LMK04816 can support the single PLL2, EXT VCO 0-delay mode by select Mode Mux 13 (R11[31:27] --> x0D) and select proper feedback clock using FBmux.

N-div values can be taken based on clock divider in 0-delay operation.

This mode provision is there in device but not validated/disclosed in datasheet. Hence, we would be recommending to confirm from your end.

Thanks!

Regards,

Ajeet Pal

Hi Ajeet,

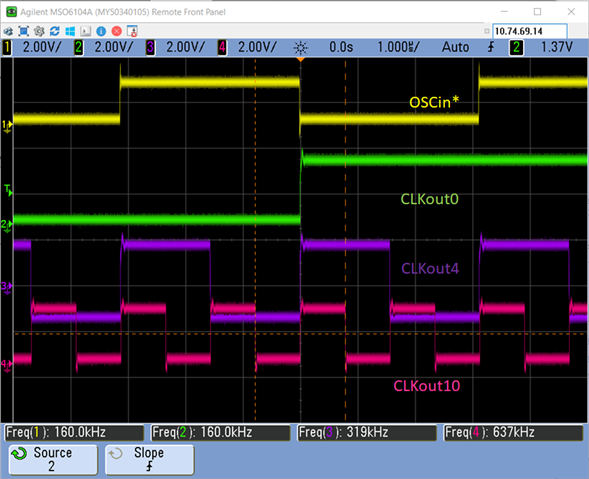

Finally I manage to test out the 0x0D mode with actual eval board (modify with external VCO).

However, I am confuse with the sync outputs.

I expect all outputs to be sync at their rising edge once it is locked and sync (digital delay = 5 for all CLLout at default).

Here's my setting:

External VCO with 0-delay with CLKout 0 as feedback clock

Input OCSiin: 160 kHz

Input Multiplier: 1

R counter: 2

fPD: 80kHz

N counter: 1

Feedback Clock Divider: 768 (CLKout 0: 80kHz)

VCO: 61.44MHz

The outputs are locked but sync at falling edge instead of their rising edge.

Am I missing anything here?

Hi Ajeet,

Sorry, forget about it.

I know why because I am probing the N channel.

Now looks good:

Hi Joe,

So I believe, you are getting the in-phase outputs from the device in external VCO 0-delay mode.

Please click, if your issue got resolved.

Thanks!

Regards,

Ajeet Pal

Hi Ajeet,

Is LMK04906 having this similar undisclosed mode?

which mean LMK04906 can also support the single PLL2, EXT VCO 0-delay mode by select Mode Mux 13 (R11[31:27] --> x0D) and select proper feedback clock using FBmux?

Hi Joe,

LMK04906 also share the same architecture as LMK04816 and it should also supposed to support the undisclosed mode Mode Mux 13. but I would verify once again from design side.

Thanks!

Regards,

Ajeet Pal