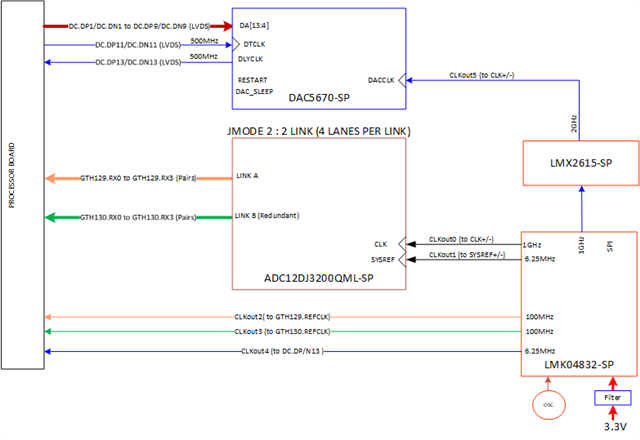

Other Parts Discussed in Thread: LMX2615-SP,

We are designing a Board for Space to be used in a Northrup Grumman space vehicle. Can you take a look at this and tell me if this will work for the CLK for both the DAC and ADC. The one thing to note is the DAC uses a 2GHs DACCLK and the data only get clocked into the A port only using the DLYCLK/DTCLK which would mean a 1GHz Data rate.