Hello,

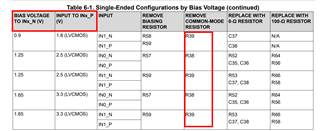

Table 6.1 of the LMK1D1216EVM user guide details the rework necessary to modify the EVM to accept a single-ended input clock. However, instead of applying an appropriate Vth level at the INx_N leg of the pair, the rework seems to be targeting the INx_P leg instead.

There are also reference designators called out (Remove Common-Mode Resistor column) that don't seem to be related to the input termination for these clock lines?

An uprev to address this table might help future readers.

Thank You,

David