Other Parts Discussed in Thread: LMX2820, LMK1D2102, LMK1D1204, CDCLVC1102

Hi

we want to use the PLL LMZ2820 as a sysref generator.

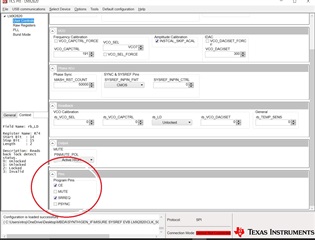

I am attaching the TICS pro configuration file: the sysref frequency is about 39 MHz and it is generated from the internal VCO.

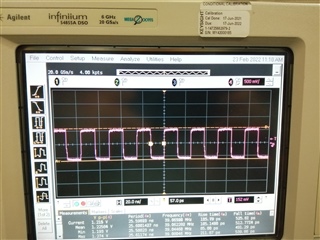

The generation of the sysref signal seems correct (see the attached measure).

But to generate this signal, the SRREQ pin needs to be HIGH. Why? The sysref comes out from the internal VCO and not from the SRREQ pins.

What is the meaning of these pins?

Thank you in advance.

Best regards,

Matteo Ricci