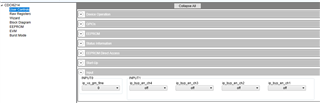

I have a technical support question regarding your CDCI6214 chip. we are using this clock generator to redistribute a single ended 125MHz clock from a phy. We are using the REFP input for the 125MHz signal, as per the datasheet, and have set the registers to get a 125 differential signal on Y1 and Y2 (P and N). The problem is that we aren't getting any clock signal on the outputs. We've used the TICS pro application to make sure that the registers are set so that the signal should be routed correctly. The configuration we use is added below, as I could not find any possibility to add attachments.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.