Hi,

We use CDCE813-Q1 as clock jitter cleaner. Both the input and output is a single ended clock and the frequency is 24.576MHz. The clock is used as the DSP reference clock.

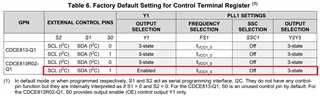

1. For CECD813R02-Q1, after power up without controlling I2C and just pull up S0 pin, the Y1 is output enable. For this use case, does the jitter cleaned function take effect?

2. The jitter of Y2 and Y3 has been shown in the datasheet, what about Y1?