- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Team,

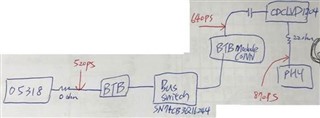

Customer wants our double check for their clock design, 05318B (LVDS) -> CDCLVP1204 (LVPECL) ->PHY (LVDS). If it looks ok to do so?

The main reason to use CDCLVP1204 instead of CDCLVD1204 is because the Tf/Tr of CDCLVP1204 is faster, customer has strict timing requirement at the end receiver PHY.

In their original PCB design, the Tr/Tf testing is over the spec Tf/Tr = 800ps max at PHY, so customer wants to do min change and see if can overcome this problem, thanks!

Andrew

Hi Andrew,

If they're already planning to use a separate device it may be simpler to use LMK1D1204 instead of CDCLVP1204. 300ps max Tr/Tf and P2P with CDCLVD1204, and the whole signal chain stays LVDS so no additional level-shifting termination is required.

I think the scheme shown with the CDCLVP1204 and appropriate termination would work, but it wouldn't be my first choice when LMK1D1204 is P2P with CDCLVD1204.

Regards,

Derek Payne