Other Parts Discussed in Thread: CDCE706, CDCE6214

Hi

I am using the CDCVF2510 at Vcc=2.5V to generate a clock to a FPGA

The FPGA requires that this clock will have a Trise of up to 500pS (10%-90%)

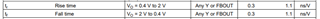

Looking at the CDCVF datasheet I see it has at Vcc=2.5V Tr minimum slewrate is 0.5V/nS. This will sum

at a rise from 0.4V to 1.7V to almost 3nS !!

With such Tr , there is no way to reach the promised Fmax of 170Mhz (5.9nS)

Even if I look at best slewrate (1.4V/nS) I am facing Tr of about 1nS, still far from the FPGA required 500pS.

Are my calculations are correct and the CDCVF best Trise at Vcc=2.5V is merely 1nS ?

If so, is there another clock generator (x5 as minimum fanout) that can meet the FPGA requirement?

Any suggestion how to improve my timing will be appreciated

Thanks

Amnon