Part Number: LMK04826

Hello,

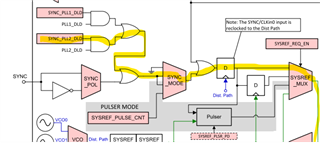

My customer is using the LMK04826 with the settings in the following config file.

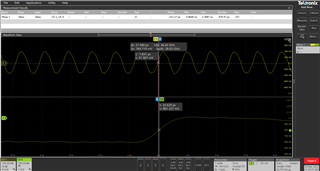

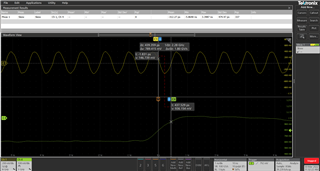

Whenever they initialize the LMK04826, there is a difference in synchronization between SYSCLK and SYSREF as shown below.

Please review the device settings to ensure consistent synchronization between SYCLK and SYSREF at all times.

Thank you.

JH