Other Parts Discussed in Thread: LMK04610

Hi,

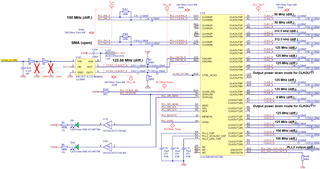

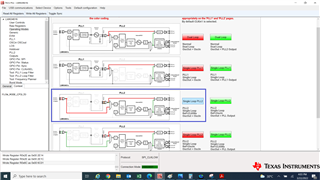

I have a custom board with LMK04616 to generate clocks. It has a 100 MHz TCXO differential clock going as input to the CLKIN0 port, a 122.88 MHz VCXO differential clock input to the OSCIN port, and an optional differential clock input via SMA to CLKIN3 port which is not used at the moment. The configuration and the output clocks desired are indicated in the attached schematic. The registers configurations I tried doesn't seem lock the PLLs for some reason. Please review the schematic for the output clocks to be generated and also for identifying issue, if any. It would be great if I could get the TICS Pro files, .TCS and register values (.TXT) for the output clocks to be generated. Thank you!