Hi Team,

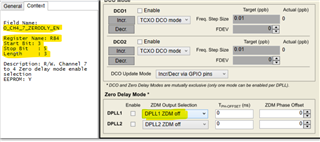

Can you advise me on how to configure ZDM using the TICSPRO.

I want to use LMK05028 to generate 148.5 MHz video clock from a 67.5 kHz reference clock.

The ratio of input and output is 1:2200.

When I tried it using the TISPRo with the Configuration file attached,

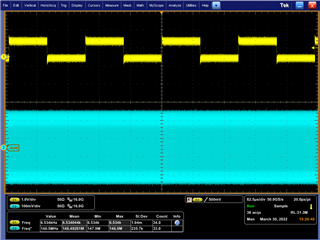

Register value for the feedback divider was different from my expectation as bellows:

DPLL2_REF_FB_DIV_BY3-By0 (R502-505) weree 0x00, 0x00, 0x02, 0xDD

( =733d instead of 275d : 2200/8)

DPLL2_REF_NUM_BY4-By0 (R506-510) were 0x53, 0xfe, 0x60, 0x1f 0xd7)

( =360,749,998,039d instead of 0)

I appreciate it if you can let me know the procedure to configure the LMH05028 in ZDM using the TICSPRO

Can you also advise me on how to configure REF_DPLL mode as well.

Mita