Other Parts Discussed in Thread: CDCE6214

Dear tech support,

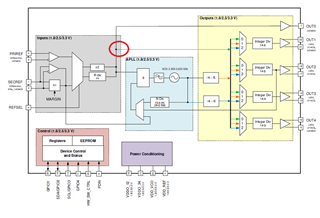

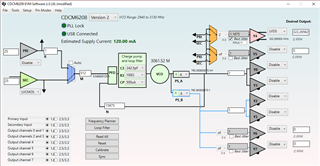

I need to provide a 322.265625 MHz or 644.53125 MHz reference clock to an Intel Cyclone 10 GX FPGA for use with an USXGMII interface. This is needed to communicate with a 10GBASE-T PHY from Marvell.

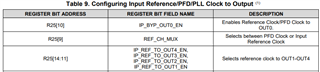

I'd like to generate such ref. clock with a CDCM6208 V2, but I can't find any clear indication on how to calculate the jitter / phase noise when using the output fractional dividers.

I see that I can't obtain the required frequency with an integer divider.

My Idea was to adopt the following configuration to obtain the desired clock. I see that the EVM software can plot the phase noise for integer divider outputs but not for fractional dividers ones.

I also need to generate other clocks, such as 100MHz, 50MHz and other aux ones which doesn't have strict jitter requirements.

Can you show me how to calculate the jitter in this case?

Is there any other TI clock generator more suitable for this application? I'd prefer a power supply of 1.8V if possible.

Thank you