Part Number: CDCE6214

Hi,

My customer has the following questions. Could you please support us?

*1.

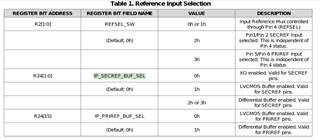

When my customer wakes up Fall-Back Mode (REFSEL=Open, HW_SW_CTRL=open), which is selected on input clock, PRIREF input or SECREF input?

He plans to connect SECREF pin with 25MHz XO and to connect PRIREF pin with pull-down. On this case, does "25MHz clock" output from CLKOUT0 pin?

Please advise us.

*2.

Under the above condition, he expects 100MHz diff clock output from OUT2 and OUT3 pins. Is his understanding correct?

But datasheet said "The PLL would not be auto-calibrated." What does this mean? Please advise us.

Thanks and best regards,

M.HATTORI