Hello,

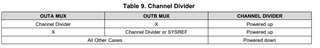

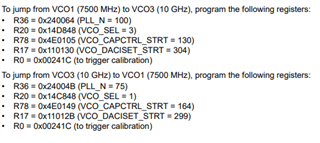

I'm seeing slower then usual lock times for frequency jumps from a VCO output to a divided down VCO output. For example, jumping from 8GHz to 7GHz has almost a x2 slower time but when I jump from 7GHz to 8GHz I see normal lock times. I verified in the PLL simulator that I should be seeing similar analog lock times, right now we're running the SPI bus at 75MHz. Trying to achieve fast lock times and when looking through documentation online (below snippet) for full assist, it shows a specific order of register writes, is that critical for faster lock times? Is there a particular way the registers need to be written when using the channel divider?

Thanks!