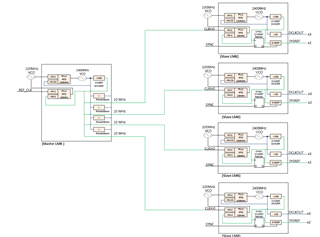

- One Master LMK04832 driving the reference clock (CLKIN0) of 4 slave LMK04832 as attached architecture above.

- The Master LMK04832 has an input reference clock to CLKIN0 and 100 MHz VCXO input to OSCIN.

- All slave LMKs will receive CLKIN0 from Master LMK output and have on-board 100 MHz VCXO input to OSCIN.

- All 4 slave LMK output clocks need to be synchronized and aligned for Multi-clock synchronization using Zero-Delay Dual-Loop Mode (ZDM), SYNC and continuous SYSREF using SYSREF_MUX mode.

Kindly verify the scheme.