Other Parts Discussed in Thread: ADC34J25

Dear product line engineer

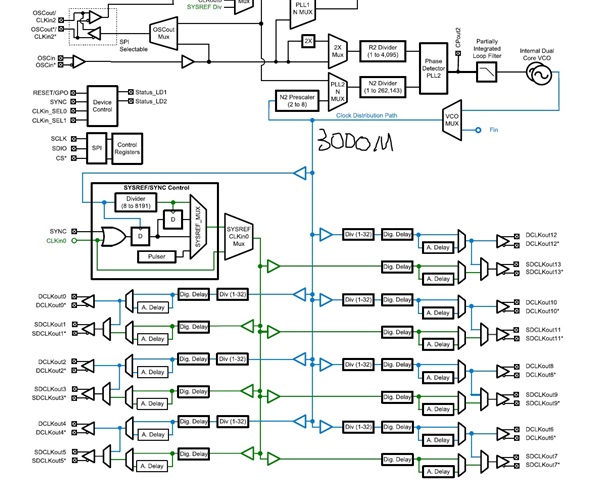

my customer has below question for LMK04828.

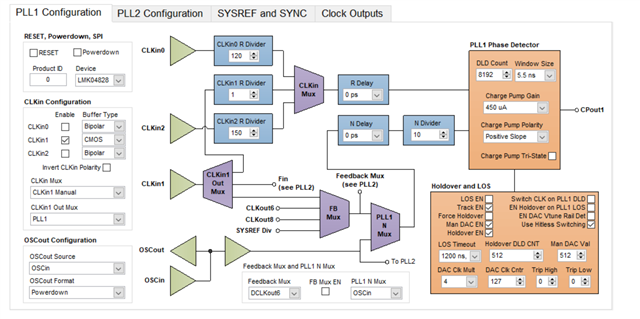

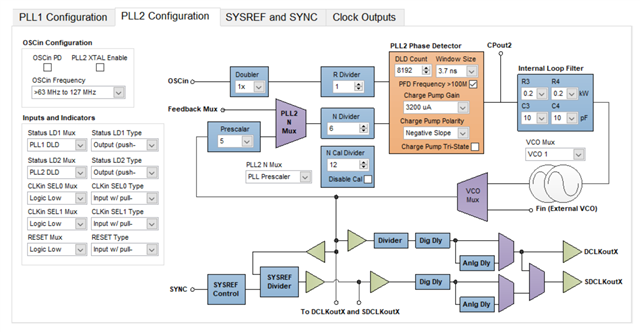

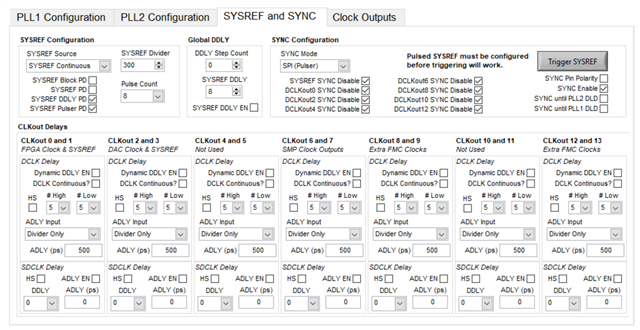

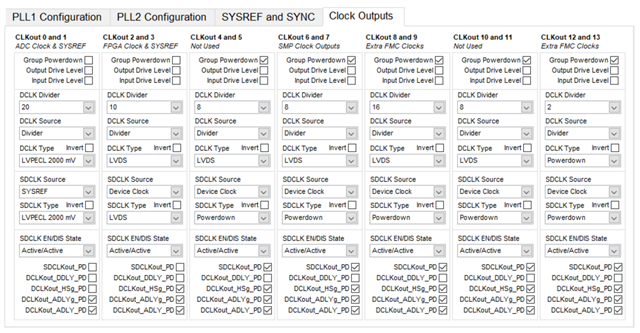

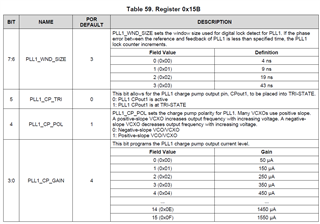

"Could you help me to double check that this device can generate 10MHz frequency for normal clock? I mean here I don’t want to use the JESD SYSREF/SYNC function."

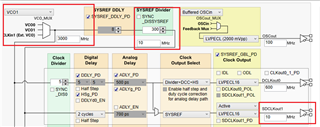

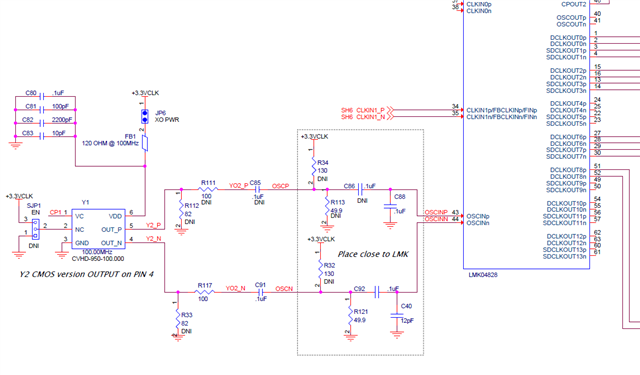

The desired VCO frequency here is 3000MHz.

thank you very much!

regards,

Bill