Part Number: LMK04610

Hello,

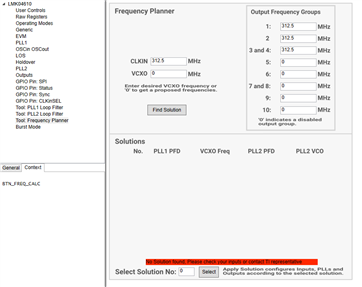

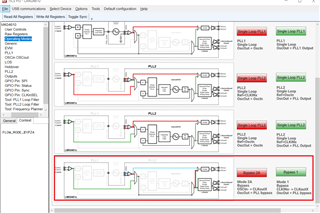

Apologies if I am missing this in the datasheet, but I am confused on how to best select a VCXO for the LMK04610 device for putting the device into jitter cleaner mode. My current application has a clock input that can vary depending on the use case of the system. If I do select a VCXO for cleaning does that limit the flexibility I can have with the input clock to the system?

Let me know if further clarification is needed.

Thanks,

Ryan