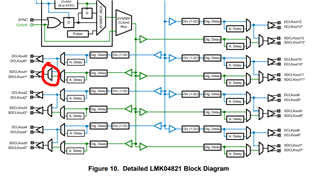

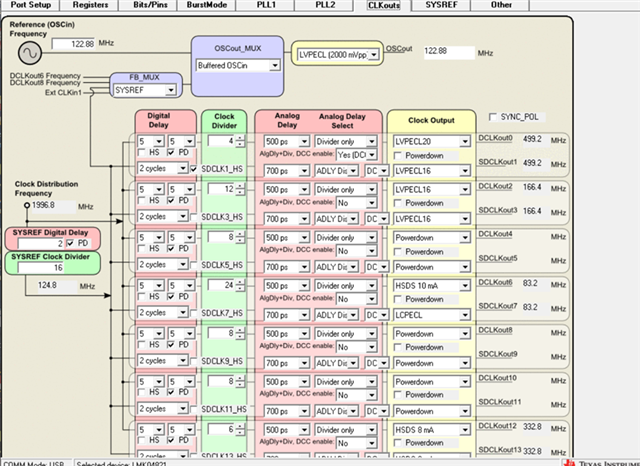

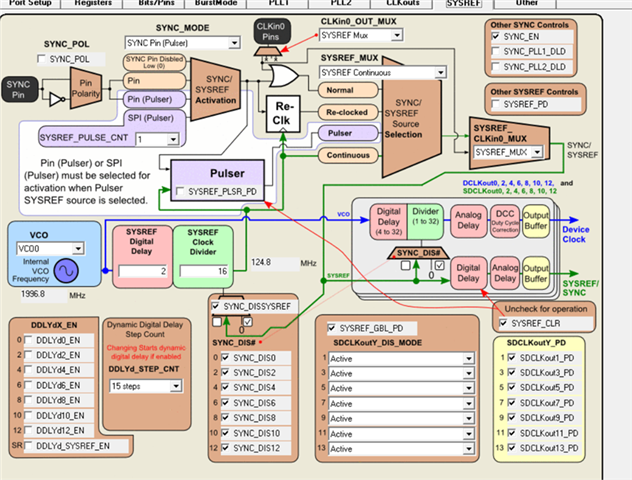

The manual explains that lmk04821 has a total of seven groups of clocks. Each group of clocks includes DCLK and sdclk, of which DCLK is affected by the clock divider parameter and the other sdclk is affected by the sysref clock divider parameter. During debugging, it is found that the output waveform in the same group of clocks is only affected by clock dividers. The configuration is as follows.Coaxial cable connection is dclk0 and sdclk1 respectively.Test with LMK04821EVM.

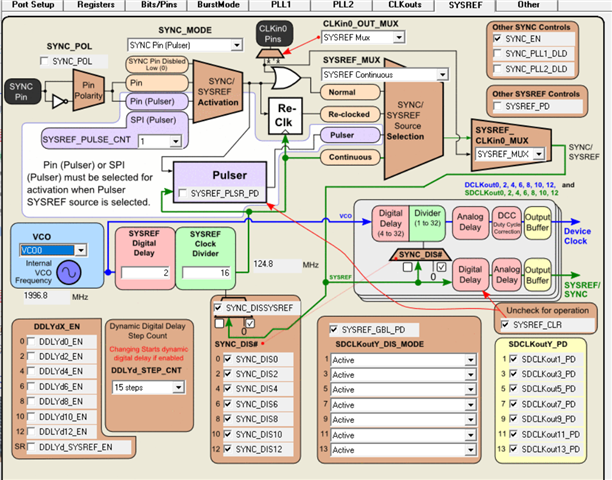

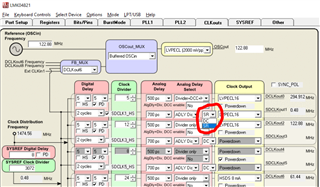

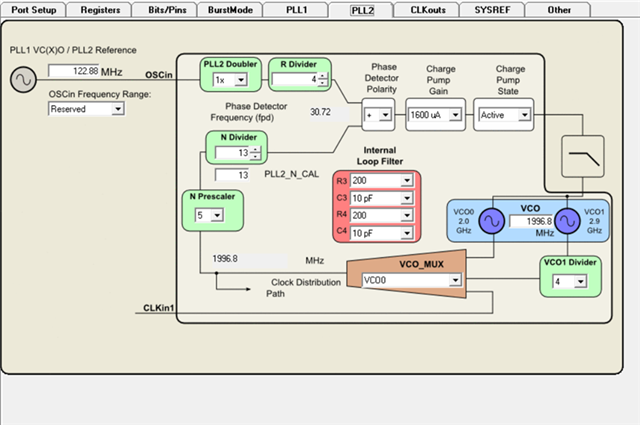

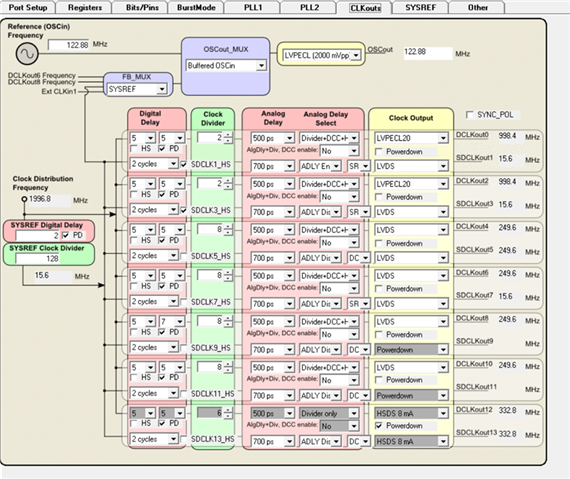

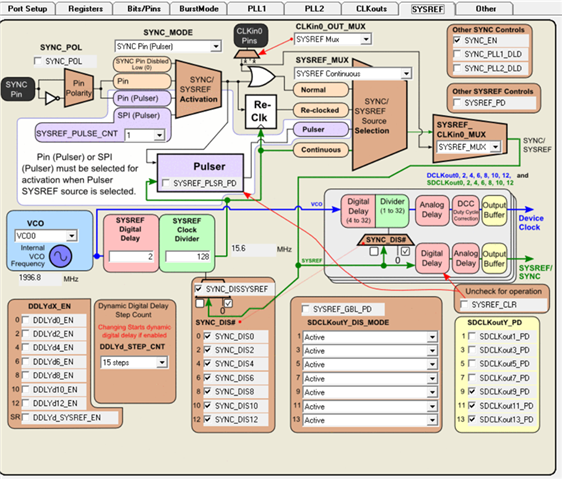

The configuration is shown below.

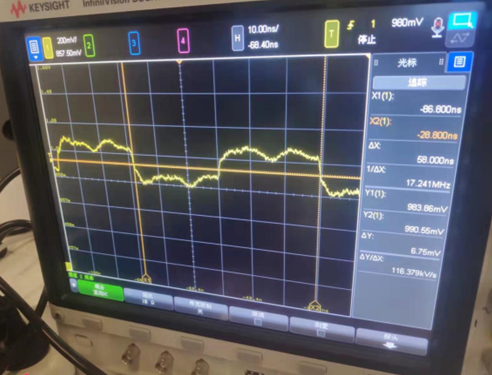

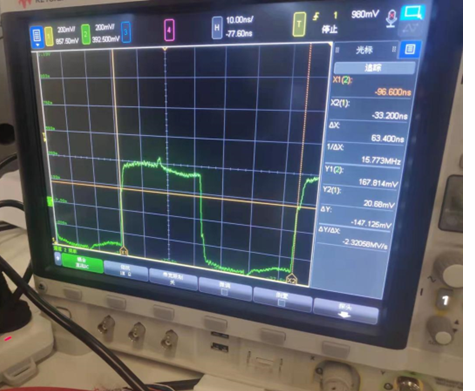

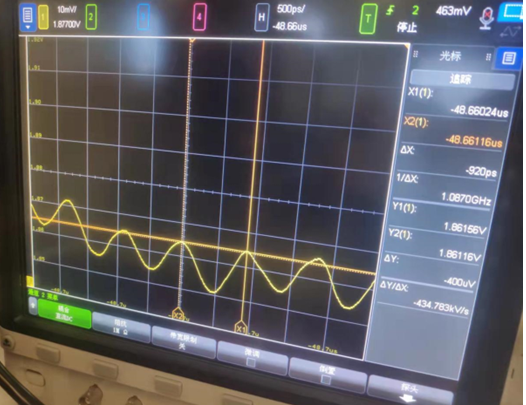

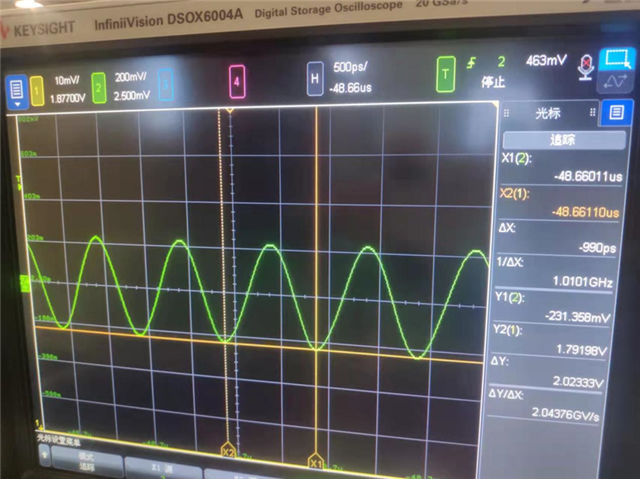

waveform is as follows: