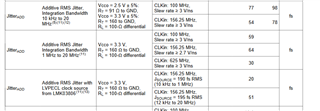

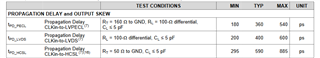

LMK00304 only has the Additive RMS Jitter parameter of 1MHz to 20MHz in HCSL output mode, is there any Additive RMS Jitter parameter of 12KHz to 20MHz (or 10KHz to 20MHz)?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.