Other Parts Discussed in Thread: CLOCKPRO,

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello Suchismita,

Unfortunately I am having my trouble loading the part profile with ClocksPro so I'm going to take a day or two. Can you provide me with your setup file in the meantime?

Regards,

Vicente

Hi Suchismita,

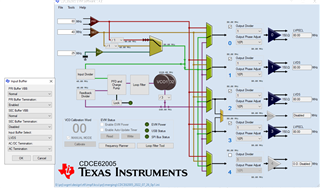

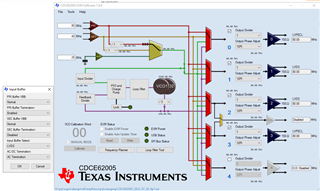

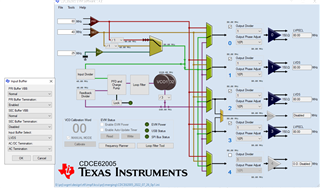

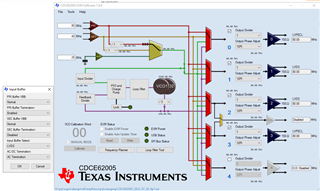

My mistake, meant the CDCE62005 GUI.

I am still waiting to be able to install the appropriate files, going to take another day or two.

Regards,

Vicente

Hello Suchismita,

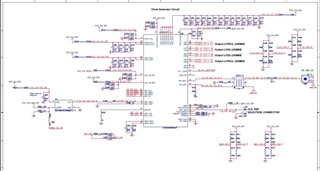

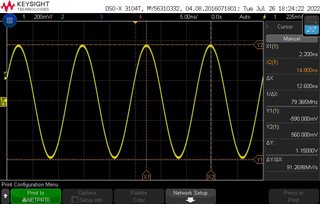

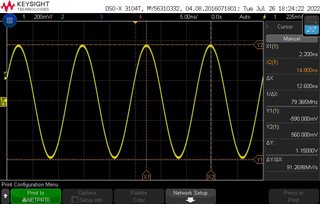

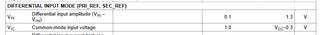

I see that the input to the CDCE62005 does not meet the required input levels. Can you please confirm?

Can you measure the input signal directly at the pins 45/46?

Did you try LVPECL as input buffer?

Regards,

Julian