Hi,

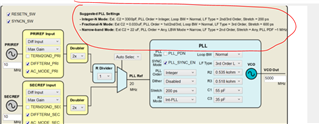

We are using the LMK03318 in our design and have started to have issues with long term reliability of the PLL lock. I've attached our

settings and we are testing this on the LMK03318EVM evaluation board, with a 10 MHz input reference.

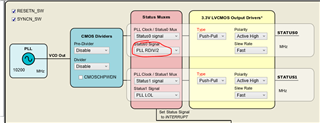

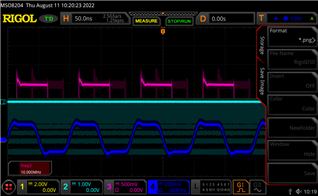

OUT7 is configured as a 10MHz clock and I am comparing to the input reference on an oscilloscope, and initially the output

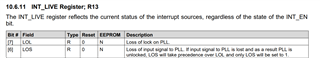

and input appeared well locked. When I enable the interrupt enable on register R17, at first there are no sticky status registers

flagged. However after leaving for several hours, the LOL_INTR and CAL_INTR flags are set and there appears to be some phase shift

between the input 10 MHz and OUT7, as seen in the below oscilloscope trace (Pink/CH3 is OUT7 from LMK, Blue/CH4 is 10MHz input reference).

We believe we have configured everything per the datasheet and EVM software requirements, but it seems like something is not well optimised. Any help is appreciated.

Thanks,

Jordan

0x0B00

0x0CDD

0x0E1D

0x0F00

0x1100

0x1200

0x1300

0x14FF

0x15FF

0x16FF

0x1703

0x1800

0x19F5

0x1B20

0x1C00

0x1D0F

0x1E00

0x1F20

0x2020

0x21F9

0x2220

0x2320

0x241F

0x2510

0x260F

0x2710

0x2807

0x2910

0x2A03

0x2B18

0x2CF9

0x2D0A

0x2E00

0x310A

0x3250

0x3303

0x3400

0x3500

0x3802

0x3918

0x3A00

0x3BFA

0x3C00

0x3D00

0x3E00

0x3F00

0x4000

0x4101

0x420C

0x4304

0x4401

0x4504

0x4607

0x4701

0x4810

0x5600

0x5800

0x59E3

0x5A01

0x5B32

0x5C01

0x5D59

0x5E01

0x5F9C

0x6001

0x61EE

0x6202

0x632E

0x6402

0x65A4

0x6603

0x670A

0x6800

0x6900

0x7308

0x7500

0x7607

0x7701

0x7800